Introduction

This assignment is a little respite from the logic kits: just answer a few questions! Note that the answers are to be written on paper, not done using

Quartus.

The Assignment

Draw diagrams for the following circuit components:

- All the gates in a 4×2 multiplexer (two OR gates, 8 AND gates, and 2 inverters); label all inputs and outputs meaningfully

- All the gates in a 3×8 decoder with Enable; label all inputs and outputs meaningfully

- All the gates in a clocked R-S latch; label all inputs and outputs meaningfully

- All the gates in a positive edge-triggered D flip-flop with Enable

- Using a symbol for the flip-flops, a 3-bit register; label all inputs and outputs meaningfully

- A complete 4×3 register file with one read port and one write port; label all inputs and outputs meaningfully; include a RegWrite control input

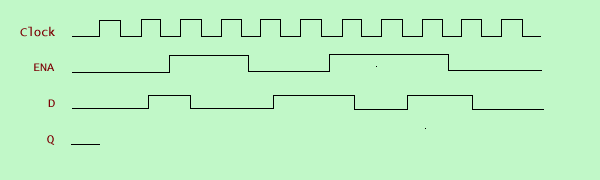

Complete the following timing diagram.

Draw arrows showing what edge of the clock causes the transitions in the value of Q. Note that Q is assumed to be initially off. Draw vertical guidelines to make your diagram clear and accurate.

Submit The Assignment

- This is a hand-in-on-paper assigment. Bring your written answers to class on the due date.

- See the course syllabus for grading and late homework policies.